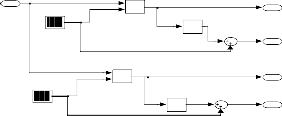

techniques we can observe in figure (C) there is a level shift when we use previous PWM techniques when it is

type of load. The

International Journal of Scientific & Engineering Research, Volume 5, Issue 1, January-2014 535

ISSN 2229-5518

S.DEVI LAVANYA1 ,Dr.D. KIRUBAKARAN2

—————————— ——————————

One advantage that multilevel inverters have compared to two level inverters is minimum harmonic distortion. A

generation of power inverters suitable for high power and high voltage applications because of reduced harmonic contents and low voltage stress across load. In this paper, a novel predictive PWM control technique is proposed for a three-phase multilevel inverter, which Controls the capacitors' voltage and load current with low switching losses. This method also controls the capacitor voltage in order to minimize switching losses. The advantage of this contribution is that it reduces the number of components highly the reason is that it uses a summer in the PWM technique which reduces the number of components also reducing single phase current and making three phase current zero. The power electronics is a device which converts DC power to AC power at required outputvoltage and frequency level is known as an inverter. The inverters can be broadly classified as two level inverters and multilevel inverters.

————————————————

1EEE, Research scholar in Prist University Tanjavur-

613403, Tamilnadu-India,1E&C Dept., Associate professor, Nadgir Institute of Engineering and technology,Bangalore-60072,Karnataka-India. devilavanyas@gmail.com.

2 Professor/EEE, St. Joseph’s Institute of Technology,

Chennai -119, Tamilnadu-India,

multilevel inverter can be utilized for multipurpose applications, such as an active power filter, a static VAR compensator; HVDC and machine drive for sinusoidal and trapezoidal current applications. This paper focuses on the analysis of PWM technique for Multilevel inverter by reducing the number of components highly this is achieved by adding summer to the PWM technique which reduces the number of components highly. A seven-level inverter had been simulated by Matlab/Simulink in different ways. The proposed topology does not use any clamping diodes which is an added advantage reducing the number of components and uses only one flying capacitor for each phase. The PWM technique employed in this topology is simple and easy to understand when compared to SVPWM which makes the circuit analysis complicated. The various switching strategies that have been proposed for synthesizing output voltage with minimum distortion, sinusoidal pulse width modulation (SPWM) strategy is employed. In this method, number of triangular waveforms is compared with a reference sinusoidal modulating signal and the switching rules for the switches are decided by the intersection of the carrier waves with the modulating signal. For a 7-level inverter, a modulating signal and 6 carrier waves are required for each phase of the inverter.

All of the carriers have the same frequency f c and different amplitude Ac, while the modulating signal has a frequency of fm and amplitude of Am. Fc should be of very

IJSER © 2014 http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 5, Issue 1, January-2014 536

ISSN 2229-5518

high value compared to fm. The amplitude of the modulated wave is greater than the amplitude of the

carrier. A seven step bridge is used for three phase inverter by using 30 switches, 10 switches for each phase. Each step is defined as a change in the time operation for each transistor to the next transistor in proper sequence.

As per [1] it requires a more number of filters and

more number of chargeable capacitor for capacitor voltage balancing. But the proposed topology reduces the number of filter and reduces the number of components highly which does not use more number of capacitors and use less number of chargeable capacitors. As the name suggests that this is a five level inverter but the output obtained is sinusoidal this is because of summer added in PWM technique. As per [2] it requires the clamping diodes to clamp the voltage to a particular value but the proposed topology does not use any diodes to clamp the voltage. The control signals used here are easy for analysis which requires the analysis of less number of switching

states. Figure. (C). Shows the output of other PWM

approaching a sinusoidal waveform. But in the proposed

PWM technique such thing does not take place a pure sinusoidal waveform without level shift can be obtained. There is level shift occurring because of level shift carrier but the proposed topology has a carrier of the form shown in figure.6. and also output shows that triangular carrier has better performance compared to ramp wave as a carrier.

The input dc voltage given to the proposed topology is equal to Vdc which is clamped to +Vdc /2 and -Vdc /2 using capacitors, which is further clamped to +Vdc /4 and -Vdc /4 for the next stage given by means of chargeable capacitor the output of which is given to the three phase load. The value of the capacitor used is 10 farads acting as a dc source. As the number of levels increases the value of the

capacitance decreases. The load used here is R and RL

IJSER

techniques we can observe in figure (C) there is a level shift when we use previous PWM techniques when it is

type of load. The

1a [l1a]

S11

S12

In1

[l11] S11

[l21] S12

In1

-T-

-T-

[l1a]

1a

[l2a]

![]()

2a

[l3a]

3a

1f

150v

-T- S11

-T-

-T- S13

-T-

1f

70v

-T- S101

-T-

-T- S103

-T-

AVabc

Iabc

S13

[l31] S13

-T-

1f

150v

S12

S14

1f

70v

S102

B a

S104 b

C c

2a [l2a]

3a [l3a]

S14

S21

[l12]

[l22]

S14

S21

-T-

-T-

300v

1f

150v

S21

-T-

-T- S23

1f

70v

S201

-T-

-T- S203

S22

[l32] S22

-T-

[l1f]

[l2f]

[l3f]

1f [l1f]

In2

S23

In2

[l13] S23

-T-

1f 2f

-T-

1f

3f

-T-

-T-

-T-

S24

[l23] S24

-T-

150v S22

S24

1f

70v

S202

S204

2f [l2f]

3f [l3f]

S31

S32

In3

S33

[l33] S31

[l14] S32

In3

[l24] S33

-T-

-T-

-T-

Discrete,

Ts = 0.002 s.

powergui

1f

150v

S31

-T-

-T- S33

-T-

1f

70v

-T- S301

-T- S303

-T-

S34

[l34] S34

-T-

1f

150v

-T-

S32

S34

1f

70v

-T-

S302

S304

IJSER © 2014 http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 5, Issue 1, January-2014 537

ISSN 2229-5518

Value of all the capacitors used is around 20 farads.

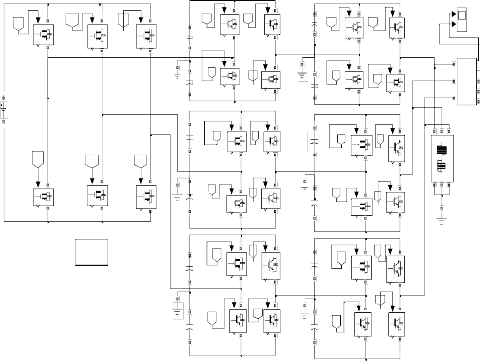

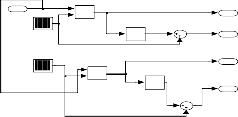

The power circuit diagram of a three phase full bridge inverter is shown in Fig (1). DC supply for three phase inverters is taken from a battery or usually from a rectifier. A circuit is obtained using 30 switches and 10 IGBTs in each phases. The proposed topology is analyzed using MATLAB/SIMULINK software using two types of load R and RL. The out voltage and current waveforms are as

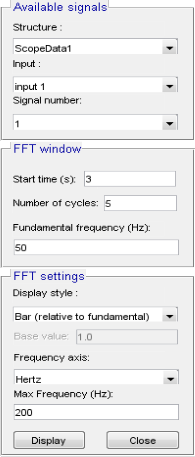

shown in Fig (5) and FFT window.

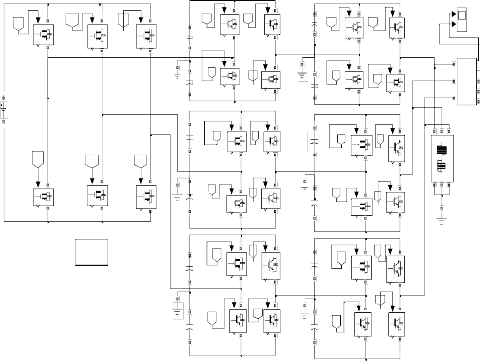

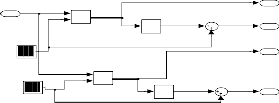

The PWM technique employed in this topology is obtained using carrier based PWM technique which is shown in Fig (2a) and Fig (2b). In this technique the sine wave is used as a reference wave which is compared with a logical comparator operator and which output is compared with a repeating sequence TRIANGULAR wave using the logical not operator the output of this is given to the summer. The amplitude of the reference required is high compared to carrier.

1 | ||||||

1a | Scope | 3 | ||||

> | NOT | 4 1f | > | 3a |

NOT

In1

S11

S12

S13

S14

S21

NOT Logi cal

Operator4

6

3f

NOT

IJSS22 ER

>

NOT

NOT

2 In2

2a

5

2f

In3

S23

S24

S31

S32

S33

S34

1

In 1

>

NOT

1

S1 1

2

S1 2

3

In 3

>

NOT

9

S3 1

3

S1 3

>

10

S3 2

NOT

4

S1 4

> 11

S3 3

NOT

12

S3 4

2

In 2

>

NOT

5

S2 1

6

S2 2

7

S2 3

>

NOT

8

S2 4

IJSER © 2014 http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 5, Issue 1, January-2014 538

ISSN 2229-5518

IJSER

IJSER © 2014 http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 5, Issue 1, January-2014 539

ISSN 2229-5518

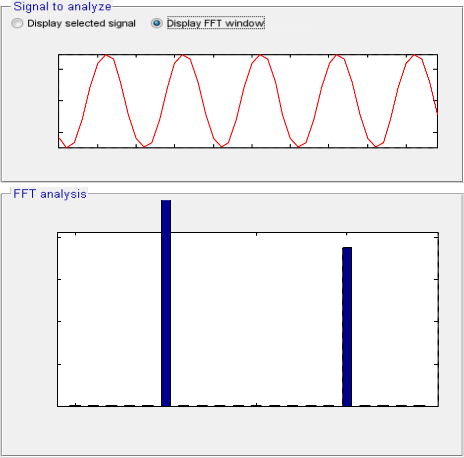

FFT window: 5 of 500 cycles of selected signal

50

0

-50

3 3.01 3.02 3.03 3.04 3.05 3.06 3.07 3.08 3.09

Time (s)

Fundamental (50Hz) = 77.39 , THD= 3.75%

4

3

2

1

0

0 50 100 150 200

Frequency (Hz)

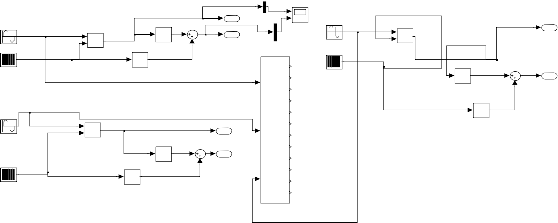

Figure (4) and (5) shows the comparison with other topologies. Figure (5) is the output of the proposed PWM technique. Figure (7) shows that the single phase current is around 2x104 amps when we use filter. Figure (C) shows that there is a level shift which does not take place in proposed topology. Figure (5) shows the three phase current is reduced to 5x10-4 and the single phase current is around 0.2amps and output voltage of around

30 volts for a dc voltage of 50volts. Figure (6) shows that the total harmonic distortion is around 3.75%.

The new PWM technique is invented in this paper which is obtained by adding summer which reduces the

IJSER © 2014 http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 5, Issue 1, January-2014 540

ISSN 2229-5518

number of components and single phase current highly

and the three phases current is reduced totally the comparison with other PWM techniques is as shown. The output is obtained using a single dc source, so this topology can be used for ac power generation using solar panels as dc source and the proposed PWM technique can be implemented for further future extension and can be extended for a n number of multilevel inverter. Since the proposed topology converts DC to AC and the output obtained is sinusoidal verified using MATLAB/SIMULINK software it can be implemented for HVDC which is a promising issue of long distance transmission as the ac power cannot be stored also it cannot be transmitted over long distances as the THD=3.75% only it can be implemented for industries also the paper has used a new NPC H-bridge inverter as the number of H-bridge inverter is added the THD can be reduced also it can be made Zero and also the three phase

current is totally zero.

[6] H. Zhang, A. von Jouanne, and A. schemes to eliminate common-mode voltages,” in Conf. Rec.IEEE-IAS

Annu. Meeting, 1998, CD-ROM.

[7] International Journal of Engineering and Technology

Volume 2 No. 7, July, 2012 ISSN:2049-3444 © 2012 – IJET Publications UK. All rights reserved. 1131 Investigations on

Three Phase Five Level Flying Capacitor Multilevel

Inverter R.Balamurugan1, S.P.Natarajan2, R.Bensraj3.

[8] M. Venu Madhav “ MATLAB based Analysis and Simulation of Multilevel Inverters” International Journal of Computer Applications (0975 – 8887) Volume 39– No.4, February 2012.

Devi Lavanya born on 15/8/1980 received the B.E. degree in EEE Department from BMSCE college VTU University in 2005 and received M.E. in

Power Electronics from Sathyabama

IJSERUniversity in 2009 and working in

[1].”Fundamentals of new diode clamped multi level inverter“ by Xiaming Yuan Iro Barbi, Senior member IEEE.

[2]. Simulation and Analysis of SVPWM Based 2-Level and 3-Level Inverters for Direct Torque of Induction Motor. International Journal of Electronic Engineering Research ISSN 0975 - 6450 Volume 1 Number 3 (2009) pp.

169–184.

[3]. I. Takahashi and T. Noguchi. A new quick response and high efficiency control strategy for an induction motor. IEEE Trans. Industry Applications. Vol. IA-22, No. 5, pp. 820-827, Sept/Oct 1986

[4] D. Rendusara, E. Cengelci, P. Enjeti, V. Stefanovic, andW. Gray, “Analysis of common mode voltage - “Neutral shift ” in PWM adjustable speed drive (MV- ASD) systems,” in Proc. IEEE PESC’99, 1999, CD-ROM.

[5] L. Palma, L. Morán, and R. Wallace, “A simple and cost effective solution to reduce motor bearing currents in PWM inverter drives,” in Proc. ISIE 2000, pp. 425–429.

NDIET as Associate professor in E&C

Department, Currently research scholar in PRIST University Tanjavur, Tamilnadu-india .Areas of interest in multilevel inverters, renewable energy sources and dc- dc converters.

Dr.Kirubakaran.D has obtained his PhD from Anna University in 2010 and M.E. from Barthidasan University in 2000. His areas of interest are AC-AC converters for induction heating. He has 13 years of teaching experience. He is a life member of ISTE.

IJSER © 2014 http://www.ijser.org