to fabricate a 3D IC consisting of multiple layers of devices.

International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013

ISSN 2229-5518

International Journal of Scientific & Engineering Research, Volume 4, Issue 5, May 2013

ISSN 2229-5518

2417

3-Dimensional Integrated Circuits

Aashana Pancholi

—————————— ——————————

s demands accelerate for increasing density, higher band widths, and lower power, many IC design teams are looking up – to 3D ICs with throughsilicon vias (TSVs). 3D ICs promise “more than Moore” integration by packing a great deal of functionality into small form factors, while improving performance and reducing costs. Threedimensional (3D) in tegration is promising technology to design integrated circuits (IC) with higher speed and smaller footprint than the ones de signed by the traditional 2D IC design technologies. The idea behind 3D ICs/SiPs is to mount two or more dice on top of each other. An individual die is now so thin that theoretically it would be possible to mount 100 on top of each other to form a cube. For the monolithic manufacturing process using epi taxy, multiple device layers are grown on the same wafer in a serial manner. Once a layer of devices and their associated in terconnect are completed, an isolation interlevel dielectric lay er (for example, SiO2) can be deposited and polished to allow another layer of devices and interconnect to continue to grow vertically. To electrically connect devices across separate pro cessed layers, 3D vias are etched through the isolation layer, and metal fillings are deposited. The same process is repeated

to fabricate a 3D IC consisting of multiple layers of devices.

Fig. 1. A 3D IC

3D packaging has been around for years—stacks of die with wirebonds, packageinpackage (PiP) design, and packageon package (PoP) design, to name a few. PoP is a widespread con figuration that combines a stack of memories on top of an ap plication processor or digital baseband. Both PiP and PoP as

semblies may be categorized as 3DICs, but neither offers the performance, power, density, and form factor of true 3DICs using TSVs. What is new is the extension of the 3D package concept into the IC side.

(a) (b)

Fig. 2. A (a.) PoP and (b.) PiP packaged IC

3D packaging saves space by stacking separate chips in a single package. This packaging, known as System in Package (SiP) or Chip Stack MCM, does not integrate the chips into a single circuit. The chips in the package communicate using offchip signaling, much as if they were mounted in separate packages on a normal circuit board. In contrast, a 3D IC is a single chip. All components on the layers communicate using onchip signaling, whether vertically or horizontally. A 3D IC bears the same relation to a 3D package that a SoC bears to a circuit board.

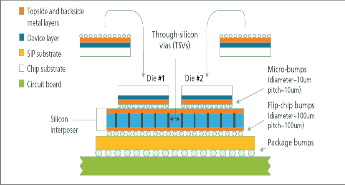

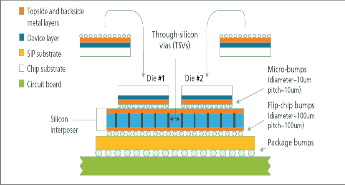

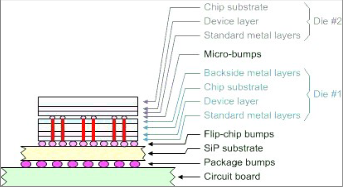

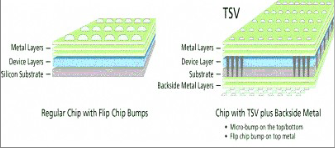

A TSV is a vertical electrical connection passing through a silicon die. TSVs are copper vias with diameters that may range from 1 to 30 microns. A “true” 3D IC using TSVs in volves two or more die connected together using TSVs. For ex ample, consider a scenario in which one die containing TSVs is attached to the SiP substrate using conventional flipchip tech nology. Meanwhile, a second die is attached to the first as il lustrated in Figure 3. The configuration for 3DIC shown here is referred to as a backtoface (B2F) configuration, because the back of the first die is attached to the face of the second die. It is also possible to have backtoback (B2B) and facetoface (F2F) configurations, especially when more than two die are stacked in this manner.

IJSER © 2013

IJSER © 2013

http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013

ISSN 2229-5518

International Journal of Scientific & Engineering Research, Volume 4, Issue 5, May 2013

ISSN 2229-5518

2418

Fig. 3. Back-to-Face Configuration of a 3D IC with TSV

TSVs are a high performance technique used to create 3D packages and 3D integrated circuits, compared to alternatives such as packageonpackage, because the density of the vias is substantially higher, and because the length of the connections is shorter. By using TSV technology, 3D ICs can pack a great deal of functionality into a small “footprint.” The different devices in the stack may be heterogeneous, e.g. combining CMOS logic, DRAM and IIIV materials into a single IC. In ad dition, critical electrical paths through the device can be drastically shortened, leading to faster operation.

Traditional singledie SoCs have some disadvantages. One is that all components are placed on the same die at the same process node, even though analog and RF design at advanced process nodes is extremely challenging. If a design team tries to implement analog circuitry at an advanced process node, it may take a great deal of time to develop and test the necessary IP blocks, as well as cope with processrelated issues such as variability and leakage. Another challenge for singledie SoCs is mixedsignal integration and verification. Placing analog and digital circuitry in close proximity can cause many prob lems. Alternatively, sensitive analog or noisy digital compon ents could be placed in a separate IC, but that makes it neces sary to drive signals between individual packages, which con sumes power and reduces performance.

In a 3D IC, a silicon interposer substrate (either passive or active) may be added to provide much finer dietodie inter connections, thereby increasing performance and reducing power consumption. A silicon interposer also includes TSVs, which provide connections from the upper metal layers to ad ditional backside metal layers.

Fig. 4. A complex 3D IC with TSV and Silicon Interposer

There are two main techniques of manufacturing a 3D IC In terms of the process and the level of assembly that 3D ICs require, : Monolithic and DieStacking .

For the monolithic manufacturing process using epitaxy, multiple device layers are grown on the same wafer in a serial manner. Once a layer of devices and their associated intercon nect are completed, an isolation interlevel dielectric layer (for example, SiO2) can be deposited and polished to allow anoth er layer of devices and interconnect to continue to grow vertic ally. To electrically connect devices across separate processed layers, 3D vias are etched through the isolation layer, and met al fillings are deposited. The same process is repeated to fab ricate a 3D IC consisting of multiple layers of devices. There is only one substrate, hence no need for aligning, thinning or bonding.

Another 3D integration technique is to stack individual 2D die layers vertically. In contrast to monolithic 3D manufactur ing, which may require many changes in current process facil ities, fabricating 3D ICs using die stacking technology can minimize the impact of altering existing manufacturing tech nology and equipment. With 3D die stacking, the candidate dies to be integrated onto the same package can be designed and manufactured separately, just as they are with a regular, existing 2D planar process with additional manufacturing pro cesses of substrate thinning and throughsilicon via (TSV) filling, if needed. Then they are bonded together by precise alignment of interdie vias and the application of thermocom pression. In general, die stacking presents three integration al ternatives: wafer to wafer, die on wafer, and die on die, each with their respective pros and cons from a cost or yield per spective.

While 3DICs with TSVs do not require a revolutionary new 3D design system, they do require some new capabilities that need to be added to existing tool sets for digital design, analog/custom design, and IC/package codesign. 3DICs re quire additional components to enable the 3D interconnec tions:

1. Redistribution layers (RDLs) are typically formed on the back side of the die. Bumps can thus be placed on both the front side and the back side.

2. TSVs can be drilled between the first metal layer and the backside RDL. TSVs may have diameters from 1 to 5 microns.

3. “Microbumps” (much smaller flipchip bumps) have to be aligned to create a data path from one die to another.

Fig. 5. Regular chip v/s. Chip with TSV

IJSER © 2013

IJSER © 2013

http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013

ISSN 2229-5518

International Journal of Scientific & Engineering Research, Volume 4, Issue 5, May 2013

ISSN 2229-5518

2419

Since many 3D stacks combine digital and analog/RF cir cuitry, a strong analog/mixedsignal capability plus a robust IC/package codesign capability and PCB layout system are critical for providing a “complete” 3DIC realization methodo logy. Without an integrated approach to 3DIC design, optim izing system cost with the shortest possible turnaround time will be challenging.

In addition, new capabilities such as the following will be needed to meet 3DIC design challenges:

∙ Systemlevel exploration

∙ 3D floorplanning

∙ 3D implementation (placement, optimization, routing)

∙ 3D extraction and analysis

∙ 3D design for test (DFT)

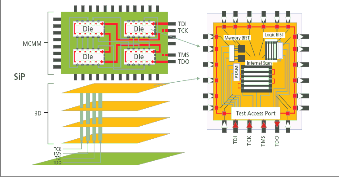

In traditional IC manufacturing, wafers are probed and in dividual dies tested (a process referred to as wafer sort) before they are packaged. In 3D integration, we are confronted with new challenges before bonding wafers. The yield of 3D ICs can be increased if we can bond pretested dies, or if we can sort the wafers first and stack matched dies (based on the speed or power consumption level) on top of each other. While wire bonded systemsinpackage (SiPs) may have a few hundred in terconnects, 3DICs may have thousands if not tens of thou sands of interconnects. Even a single defective TSV can render an entire stack unusable. If individual TSVs have 99.9% yield, at least one defective TSV can be expected in a stack of 1,000

TSVs.

A sound test methodology for 3DICs is necessary for IC designers to have the confidence to design them and to enable perbond, midbond, postbond, and postpackage (final) test ing. Fortunately, solutions are starting to emerge. 3DIC testing can leverage a large body of technology and experience with modular SoC testing by using DFT wrappers and extending them to 3D testing. In the SoC world, modular testing is made possible by DFT wrappers such as the IEEE 1149.1 boundary scan standard and the IEEE 1500 embedded core test standard. For 3DIC testing, these wrappers need to be enhanced with

3Dspecific extensions such as the following:

∙ Additional probe pads for prebond testing

∙ Test “turnarounds” that start and finish the test access points at the bottom side of each die

∙ Test “elevators” that propagate test data vertically through the stack.

Like conventional singledie IC test, 3D IC test must be con sidered at two levels – wafer test (for the silicon die), and pack age test (after die assembly into the package). The difference is that in the 3D IC fabrication, there are many more intermedi ate steps, such as die stacking and TSV bonding. This provides many more opportunities for wafer test before final assembly and packaging.

Wafer test is needed for cost optimization. If a die is bad, it

can be thrown away before it is placed in a package. If a pack agelevel test fails, the entire package would have to be thrown away. Thus, wafer test is highly desirable, especially early in the product lifecycle while defects may still be relatively high. But wafer test for 3D ICs is challenging for three reasons. First, today’s probe technology is unable to handle the finer pitch and dimensions of TSV tips, and is generally limited to hand ling several hundred probes, whereas the TSVs may have sev eral thousand probes. Second, probe technology leaves scrub marks that can potentially cause problems with the down stream bonding step. Finally, wafer test requires the creation of a knowngood die (KGD) stack. To stack knowngood die, the wafer must be thinned by about 75 percent so the tips of the TSVs can be exposed. However, as the thinned wafer is contac ted by a wafer probe, there’s a danger of damaging the wafer.

3D ICs also introduce new intradie defects. These may be introduced by new manufacturing steps such as wafer thin ning, or by bonding the top of a TSV to another wafer. Thermal effects are another potential sources of defects, be cause excessive heat may be generated from the densely packed stack of dies. Thermomechanical stress is caused by different thermal coefficients of the various materials in the stack. Despite the differences in the manufacturing steps, the resulting faults (shorts, opens, delay defects) appear to be sim ilar to what we see in conventional ICs.

Modeling defects through TSVbased interconnects is a new area. These defects may be introduced in the fabrication or the bonding of TSVs. Fortunately, defects introduced through TSVs can be mapped to existing fault models, such as opens, shorts, static, delay, and bridging faults. However, a methodology is needed to map TSV defects to known fault types.

Fig. 6. Testing Approach to a 3D IC

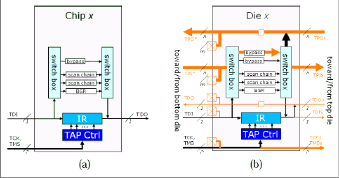

IEEE Std 1149.1 standardizes a test wrapper for chips on a Printed Circuit Board (PCB). It only has a serial mechanism, and lacks a higher bandwidth parallel test access mechanism. It has a twobit (or optional threebit) control port, consisting of the signals TCK, TMS, and optionally TRSTN. Internally, the additional control signals are generated by stepping through a

16state finite state machine named TAP Controller.

IJSER © 2013

IJSER © 2013

http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013

ISSN 2229-5518

International Journal of Scientific & Engineering Research, Volume 4, Issue 5, May 2013

ISSN 2229-5518

2420

Fig. 7. IEEE 1149.1 JTAG Wrapper for (a.) Conventional and (b.) 3D IC

The 3D enhancements are highlighted in orange and com

prise the following four items:

1. In order to support efficient highvolume testing of the die’s circuitry, a parallel, scalable test port of userdefined width n is provisioned. We refer to the inputs and outputs of this port as resp. TPI and TPO.

2. Test Turns in every die, that feed test data back to the pins in the bottom die

3. There exist many alternative uses of IEEE 1149.1 beyond boardlevel interconnect testing for purposes like silicon and software debug, emulation, incircuit programming, etc.

In VLSI circuit design, scan chains are introduced to im prove the testability of integrated circuits. After logic synthes is, all flipflops in the circuits are replaced with scan flip flops. These scan flipflops are connected sequentially to form a scan chain (or multiple scan chains) in a single chip. Each scan flip flop in the scan chain has two input sources: the output of the previous flipflop in the scan chain and the output of the com binational circuits. During normal operation, the response at the state outputs is captured in the flipflop. In testing mode, test vectors are shifted into the registers through the primary input pads and the test output values are shifted out through the primary output pads. The output values are compared with expected values to examine if the circuit is working cor rectly or not.

Although the scan chain technique offers testing conveni ence, there is an area overhead coming from both multiplexed data flipflop and the routing of the stitching wires. Long stitching wires connecting the output of each flipflop to the input of the next flipflop increase the area of the circuit, make routing difficult, and influence test performance as well. Since one of the main objectives in design for testability is to minim ize the impact of test circuitry on chip performance and cost, it is essential to minimize the wire length of a scan chain. Scan chain ordering techniques are used commonly in chip design to reduce wire length and circuit area. As technology scales, interconnect becomes the dominant source of delay and power consumption. Reducing interconnect delay and power con sumption has become a major concern in deep submicron designs. Threedimensional (3D) ICs are proposed as a prom ising solution to mitigate interconnect problems. In 3D chips,

multiple active device layers are stacked together with direct vertical interconnects, the TSVs.

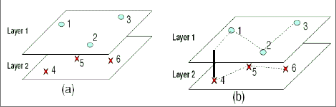

When moving from the 2D IC design to the 3D IC design domain, there are several possible methods to connect the scan chain:

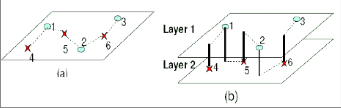

Fig. 8. (a) A conceptual example of 3D IC which has 3 scan cells to be connected. (b) VIA3D approach to connect each separate layer of scan chains via a single TSV

Advantage: Such an approach requires no change to the scan chain ordering algorithm: each layer is processed inde pendently, with a 2D scan chain ordering algorithm. The res ultant TSV number is minimized (N 1 TSVs for N layers).

Disadvantage: Because it is a locally optimized approach, it may result in the shortest scan chain for each layer, but the total scan chain length may not be globally optimized.

We call this method to be VIA3D scan chain ordering since the number of through silicon vias is minimized.

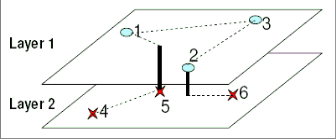

9 illustrates such an approach. After mapping the top layer nodes (Node 1, 2, and 3) onto the bottom layer, and performing

2D scan chain ordering, the scan chain order is 415263. Based on such scan chain ordering, in 3D design, if two con nected nodes are in different layers, a through silicon via (TSV) is used. In this example, there are 5 TSVs (the solid lines in the figure).

Fig. 9. Approach 2 (MAP3D): (a) All scan cells are mapped to 2D space. A 2D scan chain ordering method is then applied to the design. (b) The ordered connection is then done through TSVs.

IJSER © 2013

IJSER © 2013

http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013

ISSN 2229-5518

International Journal of Scientific & Engineering Research, Volume 4, Issue 5, May 2013

ISSN 2229-5518

2421

Advantage : Such an approach requires no change to the scan chain ordering algorithm: after mapping all the nodes to a 2D plane, a 2D scan chain ordering algorithm is applied. It is a global optimization method.

Disadvantage : The vertical distance between layers is ig nored. It may end up to using many TSVs going back and forth between layers.

We call this method to be MAP3D approach, because a 3D scan chain ordering problem is mapped to be a 2D scan chain ordering problem.

3D ordering, from which we try to find the optimal solution for minimized wire length to form the scan chain. In this ap proach, the distance function includes horizontal celltocell Manhattan distance between cells as well as vertical distance between two layers. In such case, we cannot apply a 2D scan chain ordering algorithm directly. The data structure (for ex ample, the coordinates of a scan cell) may need to be modified. However, we take into account the 3D TSV effect (the length of TSVs and the number of TSVs) in the optimization, and can have full control of the optimization process: for example, we may apply constraints on how many TSVs can be used during scan chain ordering. Fig 10 illustrates such an approach.

Fig. 10. A OPT3D approach of connecting and ordering the scan chains to optimize the minimum wire length.

Advantage : Such an approach is a true 3D scan chain or dering optimization: the length of TSVs and the number of TSVs are considered during optimization. Users have full con trol of the optimization process. It is a global optimization method.

Disadvantage : Modifications to 2D scan chain ordering al

gorithms are needed before they can be applied.

We call this method to be the OPT3D approach, because it is a true 3D scan chain ordering optimization approach.

During 3D design, one of these methods can be chosen ac cording to the requirements, such as via number limitations and the easiness to implement. For example, one may want to reserve as many TSVs as possible for signal routing or for thermal conduction, and choose the VIA3D approach. On the other hand, if minimizing scan chain length is more important, and one does not want to make the effort to change the 2D scan chain algorithm, then the MAP3D approach can be adop ted.

3D integrated circuits were proposed invented to address the scaling challenge by stacking 2D dies and connecting them in the 3rd dimension. This promises to speed up commu nication between layered chips, compared to planar layout. 3D ICs promise many significant benefits, including:

∙ Footprint

More functionality fits into a small space. This extends Moore’s Law and enables a new generation of tiny but power ful devices.

∙ Cost

Partitioning a large chip into multiple smaller dies with 3D stacking can improve the yield and reduce the fabrication cost if individual dies are tested separately.

∙ Heterogeneous integration

Circuit layers can be built with different processes, or even on different types of wafers. This means that components can be optimized to a much greater degree than if they were built together on a single wafer. Moreover, components with incom patible manufacturing could be combined in a single 3D IC.

∙ Shorter interconnect

The average wire length is reduced. Common figures repor ted by researchers are on the order of 1015%, but this reduc tion mostly applies to longer interconnect, which may affect circuit delay by a greater amount. Given that 3D wires have much higher capacitance than conventional indie wires, cir cuit delay may or may not improve.

∙ Power

Keeping a signal onchip can reduce its power consumption by 10100 times. Shorter wires also reduce power consumption by producing less parasitic capacitance. Reducing the power budget leads to less heat generation, extended battery life, and lower cost of operation.

∙ Design

The vertical dimension adds a higher order of connectivity and offers new design possibilities.

∙ Circuit security

The stacked structure complicates attempts to reverse en gineer the circuitry. Sensitive circuits may also be divided among the layers in such a way as to obscure the function of each layer.

∙ Bandwidth

3D integration allows large numbers of vertical vias between the layers. This allows construction of wide band width buses between functional blocks in different layers. A typical example would be a processor+memory 3D stack, with the cache memory stacked on top of the processor. This ar rangement allows a bus much wider than the typical 128 or

256 bits between the cache and processor. Wide buses in turn alleviate the memory wall problem.

IJSER © 2013

IJSER © 2013

http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013

ISSN 2229-5518

International Journal of Scientific & Engineering Research, Volume 4, Issue 5, May 2013

ISSN 2229-5518

2422

∙ Yield

Each extra manufacturing step adds a risk for defects. In or der for 3D ICs to be commercially viable, defects could be re paired or tolerated, or defect density can be improved.

∙ Heat

Heat building up within the stack must be dissipated. This is an inevitable issue as electrical proximity correlates with thermal proximity. Specific thermal hotspots must be more carefully managed.

∙ Design complexity

Taking full advantage of 3D integration requires sophistic

ated design techniques and new CAD tools.

∙ TSVintroduced overhead

TSVs are large compared to gates and impact floorplans. At the 45 nm technology node, the area footprint of a 10μm x

10μm TSV is comparable to that of about 50 gates. Further more, manufacturability demands landing pads and keepout zones which further increase TSV area footprint. Depending on the technology choices, TSVs block some subset of layout resources. Viafirst TSVs are manufactured before metalliza tion, thus occupy the device layer and result in placement obstacles. Vialast TSVs are manufactured after metallization and pass through the chip. Thus, they occupy both the device and metal layers, resulting in placement and routing obstacles. While the usage of TSVs is generally expected to reduce wire length, this depends on the number of TSVs and their charac teristics.Also, the granularity of interdie partitioning impacts wirelength. It typically decreases for moderate (blocks with

20100 modules) and coarse (blocklevel partitioning) granular ities, but increases for fine (gatelevel partitioning) granularit ies.

∙ Testing

To achieve high overall yield and reduce costs, separate test ing of independent dies is essential. However, tight integration between adjacent active layers in 3D ICs entails a significant amount of interconnect between different sections of the same circuit module that were partitioned to different dies. Aside from the massive overhead introduced by required TSVs, sec tions of such a module, e.g., a multiplier, cannot be independ ently tested by conventional techniques. This particularly ap plies to timingcritical paths laid out in 3D.

∙ Lack of standards

There are few standards for TSVbased 3DIC design, man ufacturing, and packaging, although this issue is being ad dressed. In addition, there are many integration options being explored such as vialast, viafirst, viamiddle; interposers or direct bonding; etc.

∙ Heterogeneous integration supply chain

In heterogeneously integrated systems, the delay of one part from one of the different parts suppliers delays the deliv ery of the whole product, and so delays the revenue for each of the 3DIC part suppliers.

∙ Lack of clearly defined ownership

It is unclear who should own the 3DIC integration and packaging/assembly. It could be assembly houses like ASE or the product OEMs.

Although 3D integration shows promise, significant chal lenges associated with efficient circuit design and operation have hampered its adoption and further development. The most important issue in 3D IC is heat dissipation. The thermal problem has already had an impact on the reliability and per formance of highperformance 2D ICs.

The problem is aggravated in 3D ICs, principally for two reasons: the devices are more packed, which results in higher power density; and the insulating dielectric layers between the device layers have much lower thermal conductivities than sil icon.

Furthermore, the third dimension brings both flexibility and difficulties to physical design algorithms. The existing 2D metrics cannot be simply extended to generate similar metrics for 3D designs. Take wirelength as an example: a ``bounding cube'' might not have enough accuracy for wirelength estima tion because of the existence of huge obstacles in zdirection.

Also, a 3D IC physical design problem is usually of higher complexity, with a much enlarged solution space due to the multiple device layer structure. Efficient 3D physical designs tools, including 3D floorplanning, placement and routing tools, are essential to 3D IC circuit design.

I would like to indeed thank my mentors and guide Mr. Arif Makrani at eInfochips, Ahmedabad, my M.tech mentor and External Guide Mr. Nirav Nanavati from eInfochips, Ahmedabad and Mr. Bhavesh Soni my M.Tech internal guide from UVPCE, Ganpat University for inspiring and guiding me towards this research topic. Its a survey paper and the contents of this paper by me is an overall survfey done on different pa pers already published and articles found on this subject. Hence I also want to acknowledge heartily each and every au thor who has done this research and helped me understand the concepts related to my survey paper.

[1] SystemLevel Comparison of Power Delivery Design for 2D and 3D ICs, Nauman H. Khan, Syed M. Alam*, and Soha Hassoun, in 3D Sys tem Integration, 2009. 3DIC 2009. IEEE International Conference, Sept. 2009

[2] 3DIC Design: The Challenges of 2.5D versus 3D, Samta Bansal, EE Times Design Article, Sept. 2011

[3] 3D TSV Test: ATE challenges and potential solutions, Ben, Scott, Kar

en, Andy, Robert, and Erik, EETimes Design Article, Oct 2011

[4] Design tools for 3D ICs remain a challenge, Ron Wilson, Electronics

Blog on Embedded.com, June,2011

[5] Test Challenges for 3D Integrated Circuits, HsienHsin S. Lee & Krishnendu Chakrabarty,

IJSER © 2013

IJSER © 2013

http://www.ijser.org

International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013

ISSN 2229-5518

International Journal of Scientific & Engineering Research, Volume 4, Issue 5, May 2013

ISSN 2229-5518

[6] Testing TSVBased ThreeDimensional Stacked ICs, Erik Jan Marinis

sen, IEEE Proceedings, March 2010

[7] Test Architecture Design and Optimization for ThreeDimensional SoCs, Li Jiang, Lin Huang and Qiang Xu. In Design, Automation & Test in Europe Conference & Exhibition, April, 2009

[8] A Standardizable 3D DfT Architecture, Erik Jan Marinissen, Chun Chuan Chi, Jouke Verbree, Mario Konijnenburg In First IEEE Intnl. Workshop on Testing ThreeDimensional Stacked Integrated Circuits (3DTEST’10) Austin, Texas, USA – November 2010

[9] 2D vs. 2.5D vs. 3D ICs 101, Clive Maxfield, EETimes Design article, Aug 2012.

[10] 2.5D ICs are more than a stepping stone to 3D ICs, Mike Santarini of

Xilinx , EETimes Design Article, March 2012

[11] Threedimensional integrated circuit, Article on Wikipedia,

[12] ThreeDimensional Integrated Circuit Design: Eda, Design And Mi croarchitectures, Yuan Xie, Jason Cong, Sachin Sapatnekar, Publisher: Springer, Publishing Date: Dec 2009

[13] ‘‘Parametric Yield Management for 3D ICs: Models and Strategies for Improvement,’’ C. Ferri, S. Reda, and I. Bahar, ACM J. Emerging Technologies in Computing Systems, vol. 4, no. 4, 2008, article no. 19.

[14] ThreeDimensional Integrated Circuits and the Future of System on Chip Designs, Robert S. Patti, Proceedings of the IEEE, 94(6):1214–

1224, June 2006.

[15] Handbook of 3D Integration – Technology and Applications of 3D In tegrated Circuits, Philip Garrou, Christopher Bower, and Peter Ramm, WileyVCH, Weinheim, Germany, August 2008.

[16] Physical aspects of VLSI design with a focus on threedimensional in

tegrated circuit applications, Dissertation report by Zeynep Dilli,

2007

[17] Fabrication Technologies for ThreeDimensional Integrated Circuits, Rafael Reif, Andy Fan, KuanNeng Chen,Shamik Das, Proceedings of the International Symposium on Quality Electronic Design (ISQED’02), 2002

[18] A Holistic Parallel and Hierarchical Approach towards DesignFor Test, C. P. Ravikumar, G. Hetherington, ITC INTERNATIONAL TEST CONFERENCE, 2004

[19] Test Strategies for 3D DieStacked Integrated Circuits, Dean L. Lewis, HsienHsin S. Lee,

[20] Testing 3D Chips Containing ThroughSilicon Vias, Erik Jan Marinis

sen, Yervant Zorian,

[21] Efficient and Effective Placements for Very Large Circuits, WerhJein Sun & Carl Sechen, IEEE Transactions of Computeraided Design of Integrated Circuits and Systems, Vol 14, No 3, March 1995

[22] Placement and Routing in 3D Integrated Circuits, Cristinel Ababei, Yan Feng, Brent Goplen, Hushrav Mogal, Tianpei Zhang, Kia Bazar gan, and Sachin S. Sapatnekar, IEEE Design & Test of Computers, Volume 22 Issue 6, NovDec,2005

[23] Sequential 3D IC Fabrication – Challenges and Prospects, Bipin Ra

jendran, VLSI Multilevel Interconnect Conference 2006.

[24] 3D ICs with TSVs—Design Challenges and Requirements, White pa

per at Cadence.com

IJSER © 2013

IJSER © 2013

http://www.ijser.org

2423